本周,在ITF USA 2019技术论坛上,全球领先的纳米电子和数字技术研究和创新中心imec展示了一款用于制造3nm逻辑技术节点的双damascene 21nm pitch测试车。

与前几代相比,该测试车的电阻-电容产品(RC)提高了30%,且不影响可靠性。在3nm及以上互连技术中实现自对准通道和自对准块等缩放增强器的需求已经得到证明。

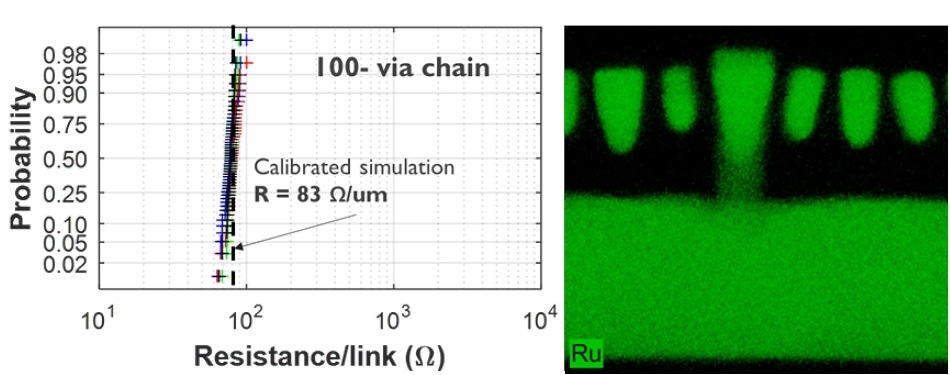

在21nm金属间距下,100个通链的每一链接的测量电阻与模拟(左)和Ru线和通孔的元素映射(右)非常吻合。

在21nm金属间距下,100个通链的每一链接的测量电阻与模拟(左)和Ru线和通孔的元素映射(右)非常吻合。

虽然传统前端技术的尺寸缩放速度预计会放缓,但行后端尺寸仍保持约0.7X的缩放速度,以跟上所需的面积缩放速度。对于3nm逻辑技术节点,M2互连层与金属间距紧密至21nm需要制造,同时保留线后端的性能。这意味着要严格控制RC延迟,同时保持良好的可靠性。

Imec首次展示了与3nm技术节点相关的双大马士革21nm金属节距测试车。测量的RC显示,与前几代相比,进步了30%。测试车辆在可靠性方面也表现良好:在330°C下,530小时内没有观察到电迁移故障,在100°C下,介电击穿(TDDB)测量显示从失效到失效的>时间为10年。

为了绘制M2层,提出了一种混合光刻方法,使用193nm浸没基自定向四极子光刻(SAQP)打印线条和沟槽,极端紫外光刻(EUVL)打印块和通过结构。该试验车实现了一种无障碍的钌(Ru)金属化方案和介电常数k = 3.0的绝缘体。

第一个结果还表明,提出的互连技术可以通过添加缩放增强器来改进,包括埋地电力轨、SuperVia、自对准块、完全自对准通道和双自对准块。

来源:https://www.imec-int.com/en/home