在Grenoble的IEEE IITC会议期间,纳米电子研究中心IMEC和Lam Research Corporation今天提出了一种用于VIA和联系的新型自下而上预填充技术。

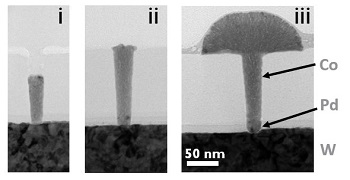

该技术基于钴(Co)的化学沉积(ELD),是一种高选择性的方法,可实现通孔和接触孔的无空洞填充。潜在地提高了电路性能,这是扩展高级互连和实现未来7纳米及以下逻辑和DRAM节点的有前途的途径。

随着逻辑和内存节点的扩展,这些高级互连的性能会受到互连电阻增加的负面影响。此外,在规模较大的孔道中出现的孔洞严重影响产量。

IMEC关于高级互连的工业联盟计划正在探索解决这些问题的新型金属化方法。解决问题的一种方法是识别集成和金属化替代方案,其在不影响可靠性和产量的情况下提供对传统技术的电阻效益。

与LAM研究一起,CO ELD技术被证明是一种可行的方法,可用于高选择性自下升高的接触填充和通过钴(CO)作为铜(Cu)的替代金属预填充物。此外,与化学气相沉积(CVD)相比,ELD工艺的高选择性,在较低的成本下,固有固有地确保良好的金属 - 金属界面,并通过填充和增加的产率来铺平无效的方式。

沟槽填充产量和线电阻也可能受益于线路和通过宽高比的解耦,允许每个用于最佳阻力/电容(RC)的设计。因此,CO PREFILLELD有可能使未来的晚期逻辑和内存技术进行扩展。

结果是与IMEC的关键合作伙伴合作实现的,作为其核心CMOS计划的一部分:GlobalFoundries,Intel,三星,SK Hynix,Sony,TSMC,Amkor,Micron,UTAC,高通公司,Altera,Fujitsu,Panasonic和Xilinx。